Built on First Principles.

ÜberNIC is not an iteration of existing ASIC designs. It is a ground-up re-architecture of the network stack, moving 100% of the logic onto the FPGA.

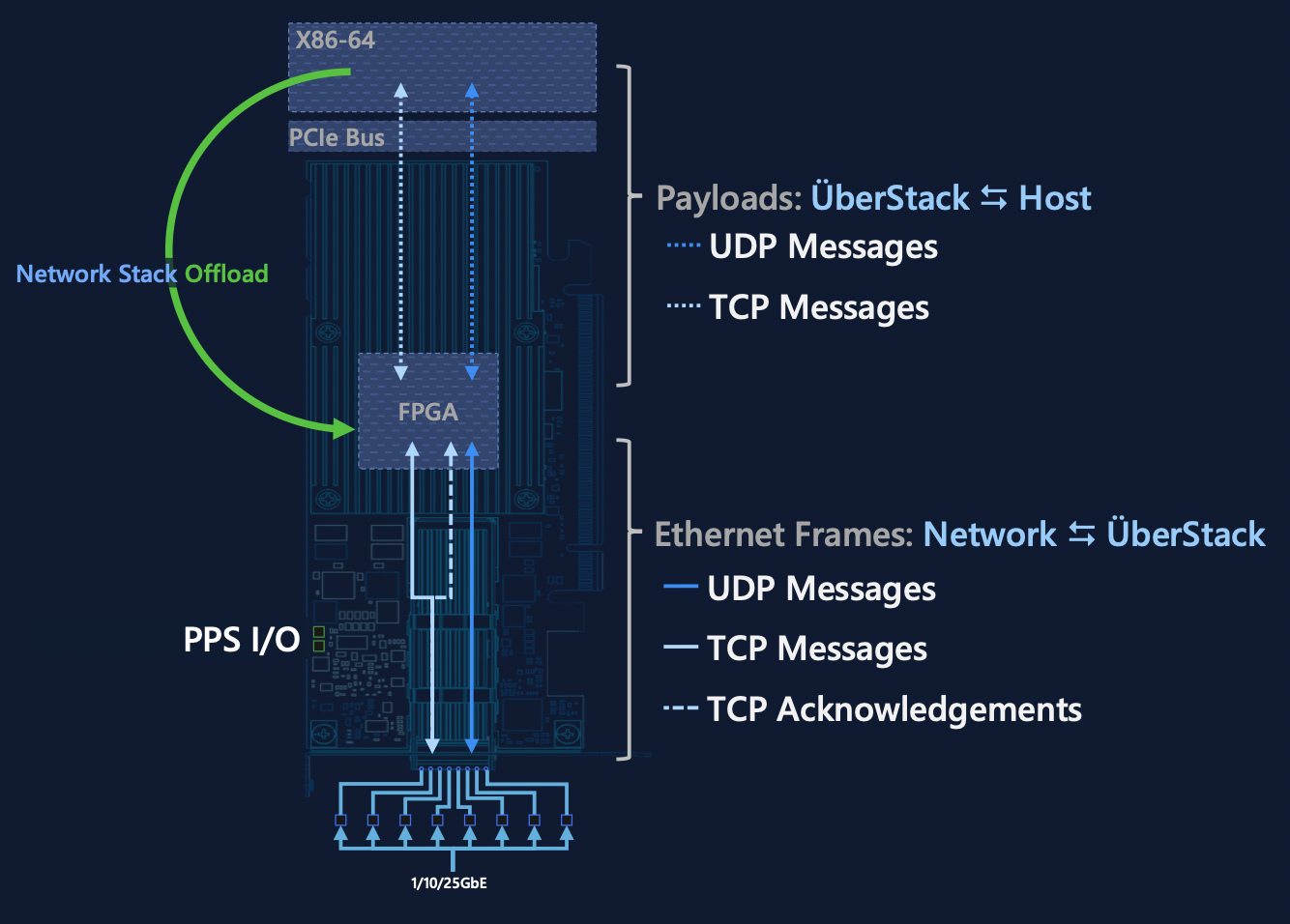

ÜberStack™ Architecture

Legacy NICs rely on the host CPU for network processing, creating interrupts, context switches, and cache thrashing.

ÜberStack changes the paradigm:

- Full Offload: MAC, IP, TCP/UDP, and Ethernet logic runs on the FPGA.

- Zero Copy: Payloads are DMA'd directly to application memory.

- Kernel Bypass: Your OS kernel is never touched during packet transmission.

Verified Performance

Data derived from the Naros.TaSR platform. Hardware timestamping at transmission and reception points. View STAC Audit →

TCP Latency — Distribution

Full latency distribution showing clustering and outliersTCP Latency — Maximum

Worst-case latency measurementsTCP Latency — Minimum

Best-case latency measurementsUDP Latency — 95th Percentile

UDP performance without protocol overheadI/O Latency Test

1) Platform: Naros.TaSR w/ÜberNIC Ultra+

2) Test: 50,000 Frames Per-Throughput Rate | 100Mbps to 10,000 Mbps @ 100 Mbps Increments | Timestamped (ns) @ "A" and "B"

3) Latency Calculation: ((Timestamp "B" – Timestamp "A") – 4m Fiber Latency)

Precision Time Infrastructure

ÜberNIC acts as the time synchronization bridge between host, CPU, and the grandmaster with unmatched precision.

Host Sync (PTM)

Deploying Precision Time Measurement (PTM) on ÜberNIC keeps the Host CPU clock synced to the NIC without software overhead or load-induced error for 95th percentile accuracy: +/- 4ns.

Infrastructure Sync (White Rabbit)

Implementation of the CERN White Rabbit protocol delivers better than 25ps synchronization accuracy over Ethernet to the time node.

Smart Data Cache Injection

Developed in collaboration with AMD for the EPYC™ Turin architecture.

In standard architecture, NICs write data to DRAM. The CPU must then wait to fetch that data from slow memory into its cache.

With SDCI: ÜberNIC injects packets directly into the CPU's L2 Cache. This eliminates the DRAM round-trip, reducing latency and ensuring the CPU (or GPU) is never starved of data.

ÜberNIC User Interface

Multiple Familiar Interfaces Plug & Play

ÜberL2

- Non-Latency-Sensitive Use-Case Kernel-Bound Support

ÜberSock

- ULL Kernel Bypass C API

- Provides Access to FPGA-Based ÜberStack & Raw Frame Functions

- Includes 13 Design Examples w/Source Code

ÜberLoad

- ULL LD_PRELOAD Kernel Bypass Socket-Compliant Interface

- Performance Indistinguishable from ÜberSock

- Provides Access to FPGA-Based ÜberStack & Raw Frame Functions

- Includes 10 Design Examples w/Source Code

ÜberFPGA

- Supports User-Logic in the FPGA Chip

- Provides Access to FPGA-Based ÜberStack Functions

- Available 2025-Q3

ÜberNIC Deployment At Scale

No External Support Tools

- Full Software-Based Interaction via PCIe Bus

- No SDK or USB Programming Cable, Blaster, JTAG, etc.

Interface Management

- Fully Integrated w/nmcli, ip, ethtool, ifconfig, and nmtui

- Intuitive Naming Convention: unic_<pcie_address>_<fiber pair>

- Supports DHCP & VLAN

System Monitoring

- Human Readable & Machine Consumable

- KPIs Include Board, FPGA, QSFP, White Rabbit, Holdover Accuracy

Logic Management

- Seamlessly Review and Update IP Logic

- Automatic Flash-to-FPGA Loading of IP Logic – No Power Cycle